Un chip gravé une bonne fois pour toutes, incapable d’apprendre quoi que ce soit de nouveau… et pourtant 73 fois plus rapide qu’un GPU Nvidia dernier cri. Voilà l’étrange paradoxe de l’ASIC pour LLM — une technologie discrète qui pourrait bien redistribuer toutes les cartes de l’intelligence artificielle. Lisez la suite, ça vaut vraiment le détour.

À retenir

- Un ASIC pour LLM est une puce dont l’architecture est figée autour d’un modèle de langage précis, contrairement aux GPU polyvalents

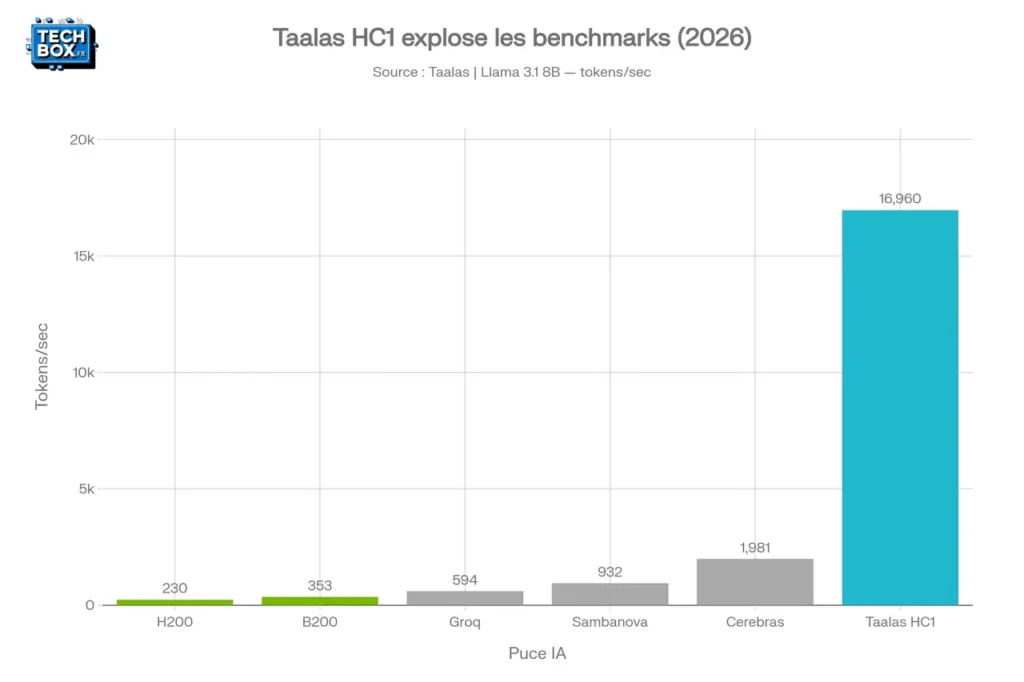

- La Taalas HC1 atteint 17 000 tokens/seconde avec moins de 1 ms de latence — contre 230 pour un Nvidia H200

- Le coût de production chute de 20x, la consommation d’énergie de 10x

- La start-up a levé 169 millions de dollars pour industrialiser la technologie

- L’horizon 2026–2030 verra trois niveaux matériels coexister : GPU d’entraînement, ASIC d’inférence cloud, et NPU edge embarqués

GPU vs ASIC : deux philosophies opposées

Pour comprendre ce qu’est un ASIC pour LLM, il faut d’abord saisir ce que fait un GPU — et pourquoi il commence à montrer ses limites. Un GPU, c’est un outil généraliste. Il peut entraîner un modèle le matin, faire du rendu 3D l’après-midi, et tourner un LLM la nuit. Cette flexibilité a un coût : énorme consommation mémoire, latence liée aux transferts entre HBM et cœurs de calcul, facture stratosphérique.

Un ASIC (Application-Specific Integrated Circuit), lui, ne fait qu’une seule chose. Mais il la fait avec une efficacité redoutable. Les ASIC pour LLM atteignent typiquement 10 à 50x de meilleures performances par watt que les GPU sur des tâches d’inférence comparables. Imaginez un couteau suisse face à un scalpel de chirurgien : le scalpel ne peut pas ouvrir une boîte de conserve, mais en salle d’opération, il n’y a pas photo.

Anecdote : en 2013, les mineurs de Bitcoin ont abandonné leurs GPU pour des ASIC spécialisés du jour au lendemain. En quelques mois, la puissance de calcul du réseau a été multipliée par mille. Même logique ici — l’histoire de l’informatique se répète, secteur par secteur.

Comment un ASIC grave un LLM dans le silicium

C’est là que ça devient vraiment fascinant. Dans un système classique, les poids du réseau de neurones sont stockés en mémoire HBM externe, puis chargés à la volée dans le GPU pour chaque calcul. Ce va-et-vient permanent est le principal goulot d’étranglement — ce que les ingénieurs appellent le “memory wall” de l’inférence moderne.

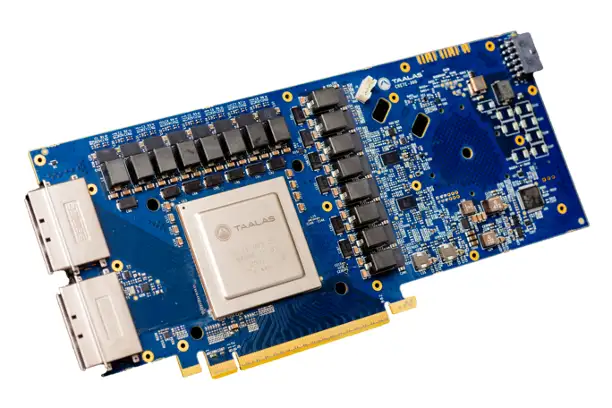

La Taalas HC1 contourne ce problème de façon radicale : les poids sont gravés directement en mémoire ROM sur le die de silicium, fabriqué sur le nœud N6 de TSMC. La puce intègre 53 milliards de transistors dans 815 mm², où chaque transistor stocke 4 bits de poids et effectue simultanément la multiplication associée. Plus de transfert, plus de latence, plus de gaspillage énergétique — tout calcul et stockage sont unifiés sur une seule puce, atteignant une densité comparable à celle de la DRAM classique.

La puce intègre également une SRAM reconfigurable qui gère le cache KV — la mémoire de contexte — et supporte des adaptateurs LoRA pour un fine-tuning léger. Le modèle de base est immuable, mais une entreprise peut tout de même l’affiner avec ses propres données. Un compromis finalement assez malin.

Des chiffres qui donnent le vertige

Voici les benchmarks d’inférence sur Llama 3.1 8B. Pour référence, le standard de l’industrie sur ce type de mesures est le MLPerf Inference de MLCommons — disponible sur mlcommons.org :

| Puce | Tokens / seconde | Coût / million de tokens |

|---|---|---|

| Nvidia H200 | 230 | ~20–50 centimes |

| Nvidia B200 | 353 | ~15–30 centimes |

| Groq | 594 | ~10 centimes |

| Sambanova | 932 | ~8 centimes |

| Cerebras | 1 981 | ~5 centimes |

| Taalas HC1 | ~17 000 | 0,075 centime |

À 17 000 tokens/seconde, le modèle génère du texte 40 à 50 fois plus vite que la vitesse de lecture humaine — la sortie est perçue comme instantanée. Forbes qualifie ces chiffres d’“insane AI inference performance” dans son analyse du 19 février 2026, signée par le spécialiste hardware Karl Freund (forbes.com). IgorSLab va plus loin : ce n’est pas un accélérateur, c’est “une déclaration de guerre”.

Les vraies limites à ne pas minimiser

Soyons honnêtes : ce tableau a ses zones d’ombre. La quantification agressive (3 bits et 6 bits) nécessaire pour graver le modèle dégrade la précision des réponses. Des tests indépendants font remonter davantage d’hallucinations et un manque de nuance sur les tâches de raisonnement profond. Et bien sûr, changer de modèle implique une nouvelle carte, voire une nouvelle puce — rigidité totale.

Anecdote : lors d’une démonstration interne, un ingénieur a demandé à une puce quantifiée en 3 bits de résoudre un problème de logique à plusieurs étapes. La réponse était fluide, confiante… et complètement fausse. La vitesse ne remplace pas la rigueur.

Taalas reconnaît elle-même que la HC1 est un démonstrateur de concept. La prochaine génération, HC2, visera une quantification en MX FP4 flottants pour rééquilibrer vitesse et qualité — et un modèle LLM de raisonnement mid-size est déjà prévu en labs courant 2026. Enfin, comme Nvidia, Taalas dépend entièrement des lignes de production de TSMC — une fragilité géopolitique non négligeable.

Edge inference : l’ASIC sort du datacenter

C’est peut-être là que l’histoire devient vraiment intéressante. D’ici 2030, le paysage hardware de l’IA devrait se stratifier en trois niveaux distincts : les GPU haute gamme pour l’entraînement, les ASIC d’inférence pour le cloud hyperscale, et des NPU edge ultra-efficaces pour smartphones, véhicules, IoT et robots. Skymizer illustre déjà cette tendance avec son IP EdgeThought, conçu pour l’on-device AI en environnement contraint.

Un ASIC autonome, insensible au brouillage, consommant 200-250 W en refroidissement à air standard, ouvre des portes que les GPU fermaient hier. Les cas d’usage concrets sont bien identifiés : traduction temps réel sur modèle stable, modération de contenu à grande échelle, assistants embarqués sans connexion réseau, drones autonomes prenant des décisions sans liaison radio. TrendForce prévoit d’ailleurs un bond de 12,8% des livraisons de serveurs en 2026, porté précisément par l’explosion de l’inférence IA et la montée en puissance des ASIC.

Le passage des GPU vers les ASIC pour l’inférence LLM ne ressemble pas à une évolution. C’est un changement de paradigme. Et comme souvent dans l’histoire de la tech, ceux qui l’ont vu venir tôt ont eu une longueur d’avance décisive.

Glossaire — Les termes clés de l’inférence IA

ASIC (Application-Specific Integrated Circuit)

Circuit intégré conçu pour une tâche unique et figée. Contrairement à un GPU généraliste, un ASIC ne peut pas être reprogrammé — mais il excelle dans sa spécialité avec une efficacité énergétique et une vitesse sans commune mesure.

Inférence

Phase d’utilisation d’un modèle IA déjà entraîné : on lui soumet une question, il génère une réponse. C’est l’opposé de l’entraînement. 90% des coûts opérationnels d’un LLM en production proviennent de l’inférence — d’où l’enjeu économique colossal de l’optimiser.

LLM (Large Language Model)

Modèle de langage massif entraîné sur des milliards de textes pour générer, traduire ou analyser du langage naturel. GPT-4, Claude, Llama ou Mistral en sont des exemples. La HC1 de Taalas grave physiquement Llama 3.1 8B dans son silicium.

Token

Unité de base traitée par un LLM — ni tout à fait un mot, ni une lettre. “Intelligence” représente environ 3 tokens. La vitesse d’un système d’inférence se mesure en tokens par seconde (t/s).

Quantification

Technique de compression d’un modèle : les poids, initialement stockés en 16 ou 32 bits, sont réduits à 3, 4 ou 6 bits. Le modèle prend moins de place et tourne plus vite, au prix d’une légère perte de précision.

Memory wall

Goulot d’étranglement structurel des GPU : les poids du modèle, stockés en mémoire HBM externe, doivent être transférés en continu vers les cœurs de calcul. Ce transfert est le principal facteur limitant la vitesse d’inférence.

HBM (High Bandwidth Memory)

Mémoire haute densité empilée directement sur le package GPU. Rapide, mais coûteuse et toujours externe aux cœurs de calcul — d’où le memory wall que les ASIC cherchent précisément à éliminer.

LoRA (Low-Rank Adaptation)

Technique de fine-tuning léger qui ajoute de petites matrices entraînables sur un modèle figé, sans modifier ses poids d’origine. Sur la HC1, la SRAM reconfigurable permet d’appliquer des adaptateurs LoRA pour personnaliser le comportement de la puce.

Edge inference

Exécution d’un modèle IA directement sur un appareil local — smartphone, drone, capteur IoT — sans passer par un serveur cloud. Réduit la latence, préserve la confidentialité, et fonctionne hors connexion.

NPU (Neural Processing Unit)

Processeur spécialisé dans les opérations de réseaux de neurones, intégré directement dans les SoC mobiles ou embarqués (Apple Neural Engine, Qualcomm Hexagon…). Cousin de l’ASIC, mais plus généraliste et reprogrammable.

TSMC (Taiwan Semiconductor Manufacturing Company)

Premier fondeur mondial de semi-conducteurs, basé à Taïwan. Fabrique les puces d’Apple, Nvidia, AMD… et Taalas. La dépendance de l’ensemble de l’industrie IA à ses lignes de production représente un risque géopolitique systémique.

MX FP4

Format de quantification flottante sur 4 bits, standardisé par le consortium OCP (Open Compute Project). La HC2, prochaine génération Taalas, l’adoptera pour améliorer la précision tout en conservant des vitesses d’inférence élevées.

FAQ — Questions fréquentes sur les ASIC pour LLM

Quelle différence entre un GPU et un ASIC pour LLM ?

Un GPU est polyvalent : entraînement, rendu, simulation. Un ASIC pour LLM est conçu exclusivement pour l’inférence d’un modèle précis — beaucoup plus rapide et moins cher à l’usage, mais impossible à reprogrammer librement.

Peut-on faire tourner n’importe quel LLM sur un ASIC ?

Non. Chaque puce est optimisée — voire gravée — pour un modèle spécifique. La HC1 de Taalas ne fait tourner que Llama 3.1 8B. Changer de modèle implique une nouvelle carte, voire une nouvelle puce.

Un ASIC pour LLM peut-il fonctionner sans connexion internet (on-device AI) ?

Oui, c’est même l’un de ses atouts majeurs. Contrairement à une inférence cloud via GPU, un ASIC embarqué fonctionne en local, sans latence réseau, sans dépendance à un datacenter — idéal pour l’edge inference en environnement contraint.

Qui fabrique des ASIC pour LLM en 2026 ?

Les acteurs notables sont Taalas (HC1), Cerebras (WSE-3), Groq (LPU), Sambanova, Etched AI (Sohu), et côté edge Skymizer (EdgeThought). Google (TPU), AWS (Inferentia) et OpenAI × Broadcom ont également leurs ASIC propriétaires.

L’ASIC pour LLM va-t-il remplacer Nvidia ?

Pas complètement. Nvidia dominera encore longtemps l’entraînement des modèles, qui nécessite une flexibilité totale. Mais sur l’inférence à grande échelle, les ASIC représentent une menace économique sérieuse : 73x plus rapides et jusqu’à 650x moins chers par token.

Source : https://taalas.com